I2C busz — hozzárendelés, eszköz, adatátvitel, címzés

Egy elektronikus áramkör létrehozásakor sok fejlesztő szembesül azzal, hogy nagyszámú köztes chipet kell használnia az egyes blokkok illesztéséhez, mintavételéhez és címzéséhez. A kiegészítő chipek számának minimalizálása érdekében a Philips már az 1980-as években egy kétvezetékes, kétirányú I2C soros hálózati interfészt javasolt, amelyet kifejezetten több chip kezelésére terveztek egyetlen eszközön belül.

Mára a Philips önmagában több mint száz I2C-kompatibilis eszközt gyárt elektronikus berendezésekhez sokféle célra: memória, videoprocesszor rendszerek, analóg-digitális és digitális-analóg konverterek, kijelző-illesztőprogramok stb.

Az I2C busz a soros adatcsere protokoll egy olyan módosítása, amely képes soros 8 bites adatok továbbítására a szokásos "gyors" módban, 100-400 kbps sebességgel. Az adatcsere folyamata itt csak két vezetéken valósul meg (a közös vezetéket nem számítva): SDA vonalon az adatokhoz és SCL vonalon a szinkronizáláshoz.

A busz kétirányúvá válik, mivel a buszra csatlakoztatott eszközök kimeneteinek kaszkádjai nyitott kollektorokkal vagy csatornákkal rendelkeznek, így replikálják az ÉS vezetékezést. Ennek eredményeként a busz minimálisra csökkenti a chipek közötti kapcsolatok számát, kevesebb szükséges tűt és nyomot hagyva a kártyán. Ennek eredményeként maga a tábla egyszerűbb, kompaktabb és technológiailag fejlettebb a gyártás során.

Ez a protokoll lehetővé teszi a címdekódolók és egyéb külső tárgyalási logikák letiltását. Az I2C buszon egyidejűleg működő chipek számát annak kapacitása korlátozza – maximum 400 pF.

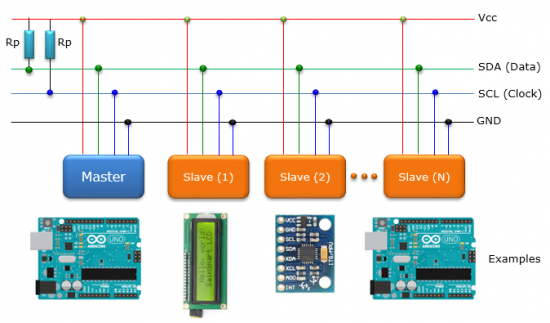

Az I2C-kompatibilis IC-k hardveres zajelnyomó algoritmussal rendelkeznek, amely még erős interferencia esetén is biztosítja az adatok integritását. Az ilyen eszközök interfésszel rendelkeznek, amely lehetővé teszi a mikroáramkörök egymás közötti kommunikációját, még akkor is, ha a tápfeszültségük eltérő. Az alábbi ábrán megismerkedhet a több mikroáramkör közös buszon keresztüli csatlakoztatásának elvével.

A buszra csatlakoztatott eszközök mindegyike saját egyedi címmel rendelkezik, ez határozza meg, és az eszköz rendeltetésének megfelelően működhet vevőként vagy adóként. Adatátvitelkor ezek az eszközök lehetnek mester (master) vagy slave (slave). A master az az eszköz, amely elindítja az adatátvitelt és órajeleket generál az SCL vonalon. A slave a masterhez viszonyítva a céleszköz.

Az I2C buszon az adott működési pillanatban csak egy eszköz működhet masterként; jelet generál az SCL vonalon.A master lehet mester vevő vagy mester adó.

A busz elvileg több különböző mastert tesz lehetővé, de korlátozásokat szab a vezérlőjelek kialakításának és a busz állapotának figyelésének jellemzőire; ez azt jelenti, hogy egyszerre több master is elkezdheti az adást, de az ilyen jellegű konfliktusok kiküszöbölhetők az arbitrációnak köszönhetően, vagyis annak, ahogyan a master viselkedik, amikor azt észleli, hogy a buszt egy másik master foglalt.

Egy pár eszköz szinkronizálását az biztosítja, hogy az összes eszköz a buszra csatlakozik, "ÉS" vezetéket képezve. Kezdetben az SDA és SCL jelek magasak.

START és STOP

A csere úgy kezdődik, hogy a master generálja a «START» állapotot: az SDA vonalon a jel magasból alacsony állapotba megy át, míg az SCL vonalon stabilan magas a szint. A buszra csatlakoztatott összes eszköz ezt a helyzetet a csere elindítására irányuló parancsként érzékeli.

Minden master egyedi órajelet generál az SCL vonalon, amikor adatokat küld a buszon.

A csere a master által STOP állapot kialakításával zárul: az SDA vonalon a jel alacsonyról magasra vált, míg az SCL vonalon stabilan magas a szint.

A vezető mindig a START és a STOP jelzések forrásaként szolgál. Amint a «START» jel rögzítve van, az azt jelenti, hogy a vonal foglalt. A vonal szabad, ha STOP jelet észlel.

A mester azonnal a START állapot deklarálása után alacsony szintre kapcsolja az SCL vonalat, és elküldi az első üzenetbyte legjelentősebb bitjét az SDA vonalnak. Az üzenetben lévő bájtok száma nincs korlátozva.Az SDA vonalon végzett változtatások csak akkor engedélyezettek, ha az SCL vonalon alacsony a jelszint. Az adatok érvényesek, és csak akkor módosíthatók, ha a szinkronimpulzus magas.

Annak nyugtázása, hogy a mester adó bájtját a szolga vevő fogadta, egy speciális nyugtázó bit beállításával történik az SDA vonalon a nyolcadik adatbit vétele után.

A VISSZAIGAZOLÁS

Tehát 8 bites adat küldése az adóról a vevőre egy extra impulzussal zárul az SCL vonalon, amikor a fogadó eszköz lemerül az SDA vonalon, jelezve, hogy a teljes bájtot megkapta.

A visszaigazolás az adatátviteli folyamat szerves része. A mester szinkronimpulzust generál. Az adó alacsony állapotot küld az SDA-nak, miközben a nyugtázó óra aktív. Amíg a szinkronimpulzus magas, a vevőnek alacsonyan kell tartania az SDA-t.

Ha a cél slave nem nyugtázza a címét, például mert éppen foglalt, akkor az adatvonalat magasan kell tartani. A mester ezután STOP jelet adhat a küldés megszakításához.

Ha a vételt a master vevő végzi, akkor az adás befejezése után - nem az utolsó bájt megerősítésével - köteles tájékoztatni a szolga adót. A slave adó feloldja az adatvonalat, hogy a master STOP jelet vagy ismétlődő START jelet tudjon kiadni.

Az eszközök szinkronizálását az biztosítja, hogy az SCL vonalra történő csatlakozások "ÉS" elv szerint történnek.

A masternek nincs kizárólagos joga az SCL vonal alacsonyról magasra való átmenetének szabályozására.Ha a slave-nek több időre van szüksége egy fogadott bit feldolgozásához, önállóan alacsonyan tarthatja az SCL-t, amíg készen áll a következő adatbit fogadására. Az SCL vonal ilyen helyzetben alacsony lesz a leghosszabb alacsony szintű szinkronimpulzus időtartama alatt.

A legalacsonyabb tartós alacsony értékkel rendelkező eszközök tétlen maradnak a hosszú időszak végéig. Amikor az összes eszköz befejezte az alacsony szinkronizálási időszakot, az SCL magas lesz.

Az összes eszköz magas órajelet kezd, és az első eszköz, amely befejezi a periódusát, az elsőként állítja alacsonyra az SCL vonalat. Ennek eredményeként az SCL alacsony állapotának időtartamát az egyik eszköz szinkronizálási impulzusának leghosszabb alacsony állapota határozza meg, a magas állapot időtartamát pedig az egyik eszköz legrövidebb szinkronizálási ideje határozza meg. eszközöket.

A szinkronizáló jeleket a vevőkészülékek használhatják az adatátvitel bit- és bájtszintű vezérlésére.

Ha az eszköz képes nagy sebességgel bájtokat fogadni, de bizonyos időbe telik a fogadott bájt tárolása vagy a következő bájt fogadására való felkészülés, akkor továbbra is alacsonyan tarthatja az SCL-t egy bájt fogadása és nyugtázása után, kényszerítve a az adót készenléti állapotba.

A beépített hardveráramkörök nélküli mikrokontroller például bitszinten lelassíthatja az órajelet alacsony állapotuk időtartamának növelésével, így a master eszköz adatátviteli sebességét a vezérlőegység sebessége határozza meg. lassabb készülék.

CÍMZÉS

Minden I2C buszra csatlakoztatott eszköznek egyedi programcíme van, amelyen a mester egy adott parancs elküldésével megcímzi azt. Az azonos típusú mikroáramköröket egy címválasztó jellemzi, amelyet vagy a szelektor digitális bemenetei, vagy analóg formában valósítanak meg. A címek fel vannak osztva a buszra csatlakoztatott eszközök címterébe.

A normál mód hétbites címzést feltételez. A címzés a következőképpen működik: a «START» parancs után a master elküldi az első bájtot, amely meghatározza, hogy melyik szolga eszköz szükséges a masterrel való kommunikációhoz. Van egy közös hívási cím is, ami a buszon lévő összes eszközt meghatározza, erre minden eszköz (elméletileg) nyugtával válaszol, de a gyakorlatban ez ritka.

Tehát az első bájt első hét bitje a slave cím. A legkisebb jelentőségű bit, a nyolcadik, az adatküldés irányát jelzi. Ha van egy «0», akkor az információ a mastertől erre a slave-re lesz írva. Ha «1», az információt a master olvassa be ettől a slave-től.

Miután a master befejezte a címbájt elküldését, minden slave összehasonlítja a címét azzal. Bárki, akinek ugyanaz a címe, szolga, és szolga adóként vagy szolga vevőként van definiálva, attól függően, hogy a címbájt legkisebb jelentőségű bitje mekkora érték.

A slave cím tartalmazhat rögzített és programozható részeket. Elég gyakran sok azonos típusú eszköz működik egy rendszerben, ekkor a cím programozható része maximum azonos típusú készülékek használatát teszi lehetővé a buszon. Az, hogy a címbájtban hány bit programozható, a chipen lévő szabad tűk számától függ.

Néha elegendő egy tű a programozható címtartomány analóg beállításával, például az SAA1064 - egy LED-jelző meghajtó, amely pontosan ilyen megvalósítással rendelkezik. Egy adott láb potenciálja határozza meg a chip címterének eltolását, hogy az azonos típusú chipek ne ütközzenek ugyanazon a buszon. Az I2C buszt támogató összes chip tartalmaz egy címkészletet, amelyet a gyártó a dokumentációban ad meg.

Az «11110XX» kombináció 10 bites címzésre van fenntartva. Ha elképzeljük az adatcserét a «START» parancstól a «STOP» parancsig, az így fog kinézni:

Itt az egyszerű és kombinált adatcsere-formátumok megengedettek. A kombinált formátum azt jelenti, hogy a «START» és «STOP» között a master és a slave vevőként és adóként működhet, ez például a soros memóriakezelésben hasznos.

Hagyja, hogy az adatok első bájtja egy memóriacímet vigyen át. Ezután a «START» parancs megismétlésével és a slave cím kiolvasásával a memóriaadatok működni fognak. A korábban elért cím automatikus növelésére vagy csökkentésére vonatkozó döntéseket az eszköz fejlesztője hozza meg, miután előzetesen tanulmányozta a chip dokumentációját. Így vagy úgy, miután megkapta a START parancsot, minden eszköznek vissza kell állítania a logikáját, és fel kell készülnie arra, hogy a cím most el lesz nevezve.